# MATLAB&SIMULINK®

#### **How to Contact MathWorks**

Latest news: www.mathworks.com

Sales and services: www.mathworks.com/sales\_and\_services

User community: www.mathworks.com/matlabcentral

Technical support: www.mathworks.com/support/contact\_us

T

Phone: 508-647-7000

The MathWorks, Inc. 1 Apple Hill Drive Natick, MA 01760-2098

HDL Coder™ Release Notes

© COPYRIGHT 2012-2022 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### **Trademarks**

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

MathWorks products are protected by one or more U.S. patents. Please see www.mathworks.com/patents for more information.

# Contents

#### R2022a

| Model and Architecture Design 1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HDL optimized arithmetic operations Additional functions for MATLAB function blocks that have MATLAB Datapath architecture Counter reuse from serialization Changes in HDL coding standards Enhanced HDL Model Advisor checks  1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Block Enhancements 1-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

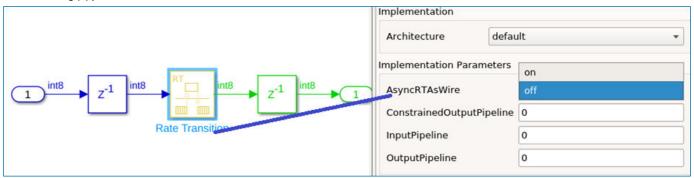

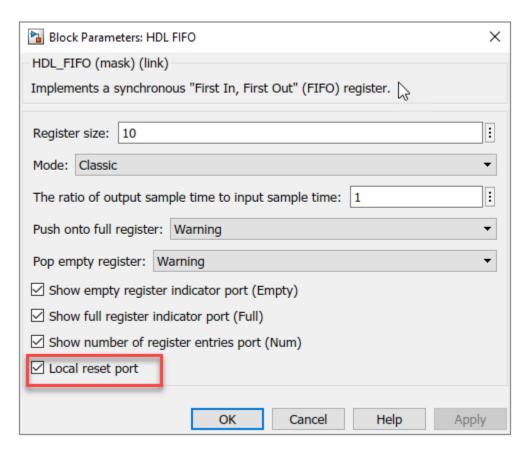

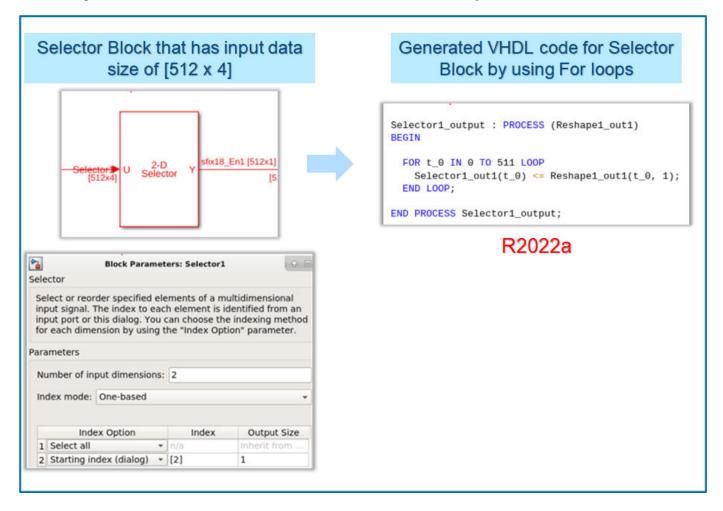

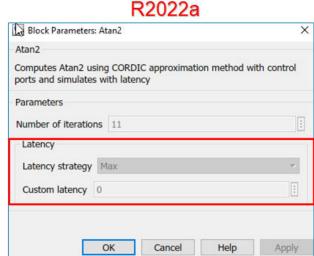

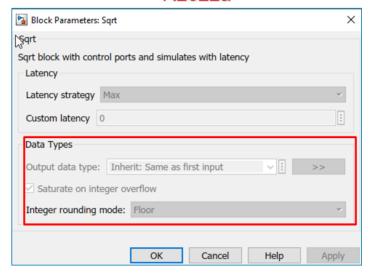

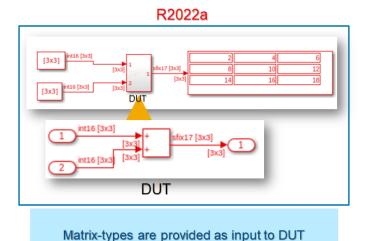

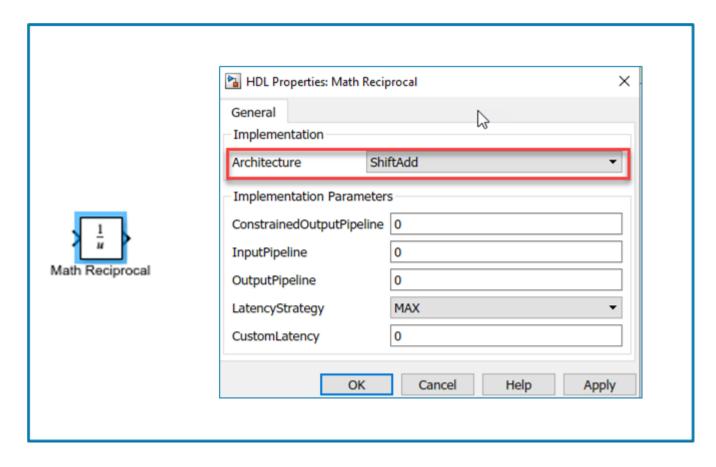

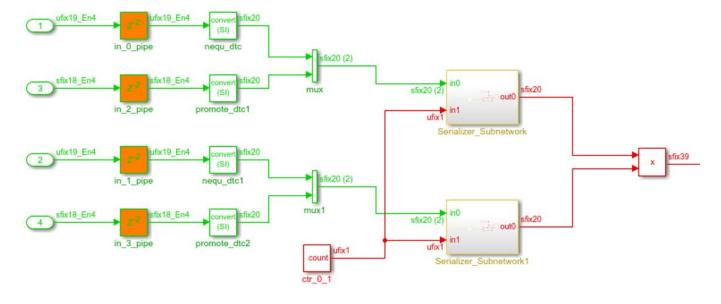

| Option for preserving logic connected to Terminator block  MinMax block streaming and min and max function vector inputs  If and Switch Case Action blocks support  HDL code generation for variable integer Delay block  HDL Property 'RAMDirective' for HDL FIFO block  HDL Block Property 'AsyncRTAsWire' added for Rate Transition block  Local Reset Port for HDL FIFO block  For-Generate loops for Selector block  n-Dimensional lookup table  Enhancements in trigonometric blocks that use CORDIC-based  approximation method  Enhancements in HDL Math library blocks  Improved HDL code generation for Serializer1D and Deserializer1D blocks  Matrix types support for design under test (DUT)  Shift-Add architecture for reciprocal function in Math Function Block  1-14  Logic guarding index access preservation  1-14 |

| Code Generation and Verification 1-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

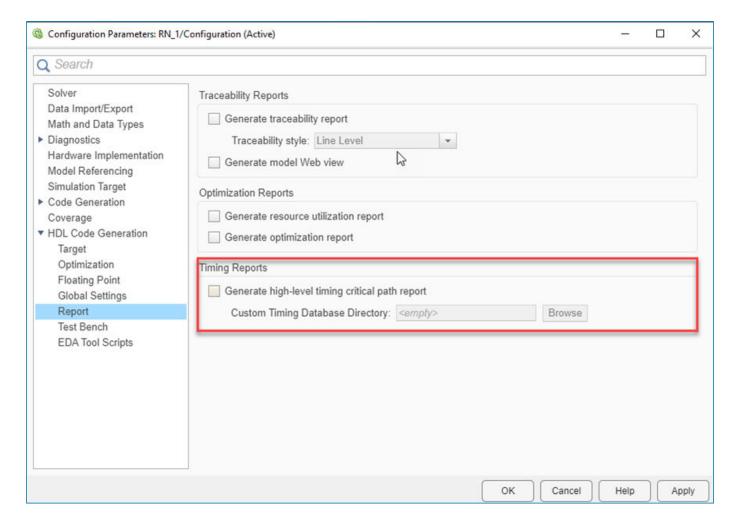

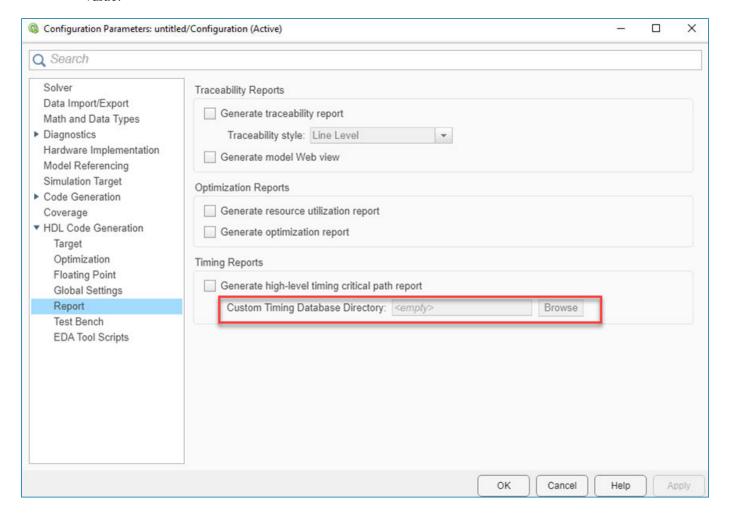

| Clock frequency specification in MATLAB to HDL Workflow Advisor 1-15 Indexing for scalarized port naming 1-15 Generation of traceability report in Japanese language 1-15 Improved critical path estimation 1-15 Enhancements to genhalltab function 1-16 Out-of-bounds error suppression during ModelSim simulation 1-17 SystemC Code Generation from MATLAB Code 1-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Speed and Area Optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Streaming and sharing area optimization improvements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Hierarchical clock-rate pipelining improvements                                                                                                                                                                                                                | 1-22<br>1-22                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| IP Core Generation and Hardware Deployment                                                                                                                                                                                                                     | 1-23                                 |

| HDL Coder Support for Xilinx Versal Devices: Generate IP core and deploy reference designs on Xilinx Versal devices                                                                                                                                            | 1-23                                 |

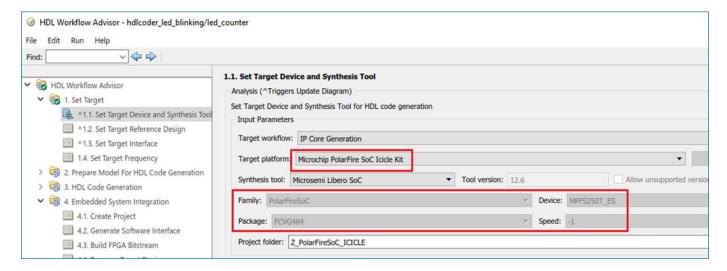

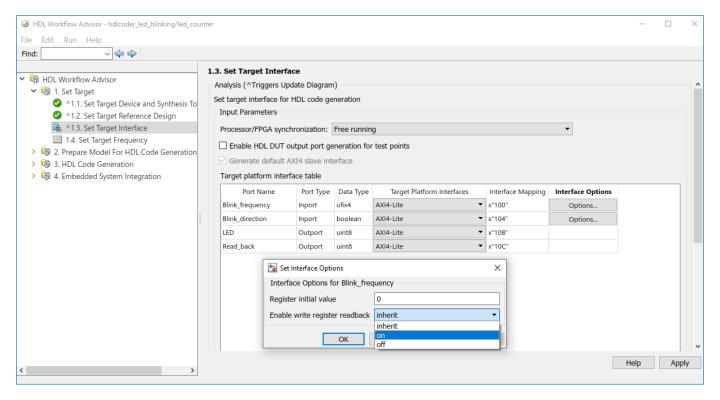

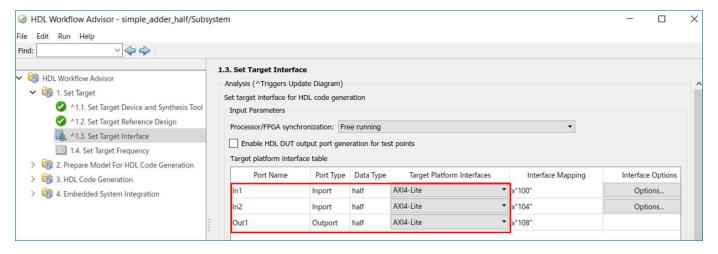

| SoC devices                                                                                                                                                                                                                                                    | 1-23<br>1-24<br>1-25<br>1-25<br>1-25 |

| Advisor                                                                                                                                                                                                                                                        |                                      |

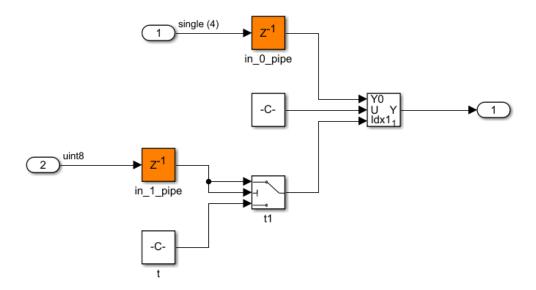

| Single-Precision data types for AXI4 stream interface in IP core generation                                                                                                                                                                                    | 1-27                                 |

| workflow                                                                                                                                                                                                                                                       | 1-28<br>1-28<br>1-28<br>1-28         |

| Simscape Hardware-in-the-Loop Workflow                                                                                                                                                                                                                         | 1-30                                 |

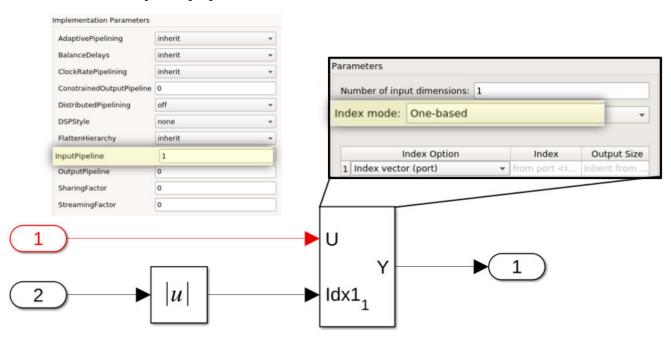

| Optimal value of oversampling factor for nonlinear Simscape models Optimization of mode vector to index subsystem for higher clock frequency                                                                                                                   | 1-30                                 |

| Simscape to HDL Workflow Reference Applications                                                                                                                                                                                                                | 1-30<br>1-30                         |

| R20                                                                                                                                                                                                                                                            | 21b                                  |

| Model and Architecture Design                                                                                                                                                                                                                                  | 2-2                                  |

| RAM style attributes for Intel/Altera and Microchip                                                                                                                                                                                                            | 2-2<br>2-2<br>2-2<br>2-2             |

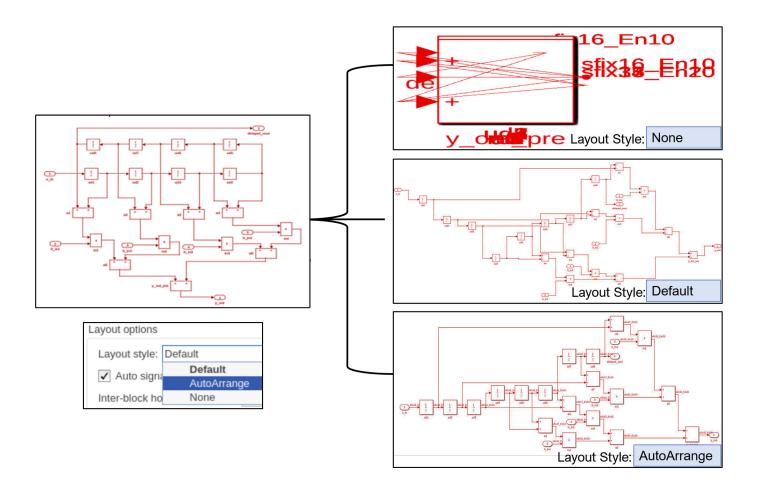

| the same variable in multiple cascaded conditional regions Layout choices for model generation                                                                                                                                                                 | 2-3<br>2-3                           |

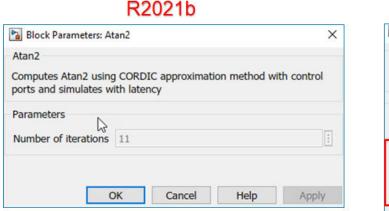

| Block Enhancements                                                                                                                                                                                                                                             | 2-5                                  |

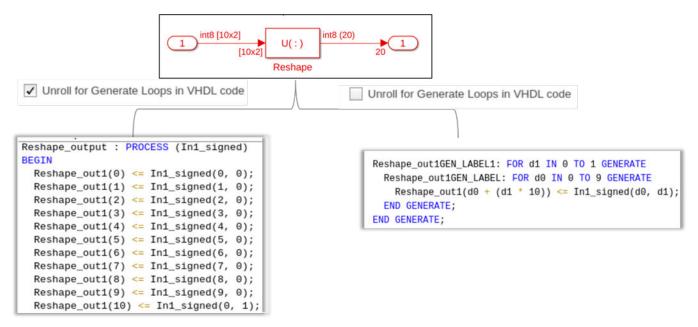

| Newton-Raphson algorithm for Math Reciprocal block  Magnitude square function in Math Function block  Half-precision data types for MATLAB Function block  Double-Precision data types for Logarithmic block  For-Generate loops for Reshape and Concat blocks | 2-5<br>2-5<br>2-5<br>2-5<br>2-5      |

|    | Fixed-point output types for Divide block and Reciprocal block                                                     | 2-6          |

|----|--------------------------------------------------------------------------------------------------------------------|--------------|

|    | Enhanced HDL math library                                                                                          | 2-6          |

|    | 4-D and 5-D lookup table support                                                                                   | 2-7          |

|    | Improved denormal optimizations for half-precision data types                                                      | 2-7          |

|    | Improved multiplier partitioning DSP QoR                                                                           | 2-7          |

|    | Reset minimization in Native Floating-Point (NFP) for ASIC                                                         | 2-7          |

|    | Set-Reset (SR) flip-flops                                                                                          | 2-7          |

|    | HDL Code Generation for Discrete State-Space block                                                                 | 2-8          |

|    | Trigger and event modes for subsystems, MATLAB Function blocks, and                                                |              |

|    | Stateflow blocks                                                                                                   | 2-8          |

|    | Wireless HDL Toolbox Reference Applications: Implement 5G NR SIB1                                                  | 2.0          |

|    | recovery, WLAN receiver, and DVB-S2 PL header recovery                                                             | 2-8          |

|    | Wireless HDL Toolbox Blocks: Model WLAN LDPC decoder, CCSDS RS                                                     | 2.0          |

|    | decoder, DVBS2 symbol demodulator, and APP decoder                                                                 | 2-8          |

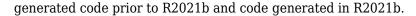

|    | Multipixel-Multicomponent Video Streaming: Implement color space                                                   |              |

|    | conversion and demosaic interpolation algorithms for high-frame-rate                                               | 2.0          |

|    | color video                                                                                                        | 2-9          |

|    | Reflection radding: rad image frames by reflecting around the edge pixer                                           | 2-9          |

|    |                                                                                                                    | 2-3          |

| Co | de Generation and Verification                                                                                     | 2-11         |

| CU | de Generation and Vermication                                                                                      | 2-11         |

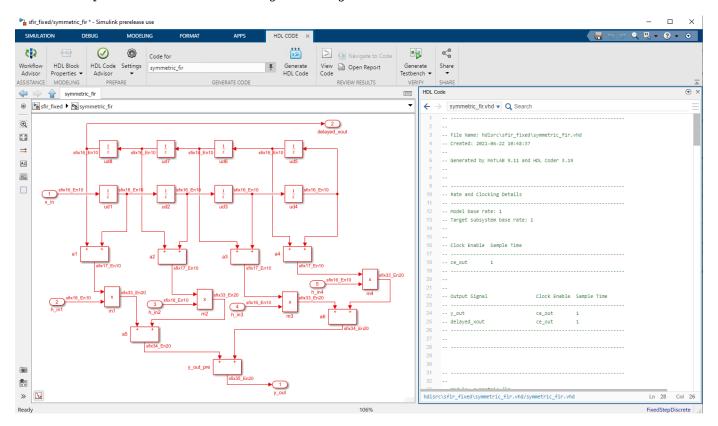

|    | Code View: View your generated HDL code directly in Simulink model                                                 |              |

|    | window                                                                                                             | 2-11         |

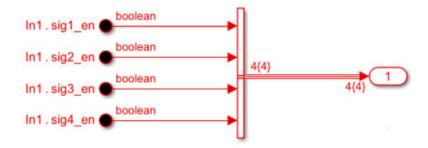

|    | Stateflow multicycle path enhancements                                                                             | 2-11         |

|    | Register-to-register path info option not recommended in HDL Coder                                                 | 2-12         |

|    | Execute chart at initialization option for Stateflow charts                                                        | 2-12         |

|    | HDL code generation performance improvement for matrix multiplication                                              |              |

|    |                                                                                                                    | 2-12         |

|    |                                                                                                                    |              |

| Sp | eed and Area Optimizations                                                                                         | 2-14         |

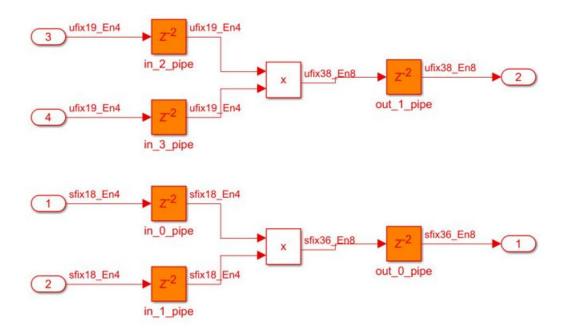

|    | Enhanced sharing and streaming optimizations for matrix-types                                                      | 2-14         |

|    | User control for tunable parameter processing and improve code generation                                          |              |

|    | time                                                                                                               | 1<br>2-14    |

|    | Improved zero-protection in Simulink-to-HDL                                                                        | 2-14         |

|    | Minimize intermediate initialization of variables in generated HDL code                                            | 2-1-         |

|    | 1.1111111120 Intermediate initialization of variables in generated 1150 code                                       | 2-15         |

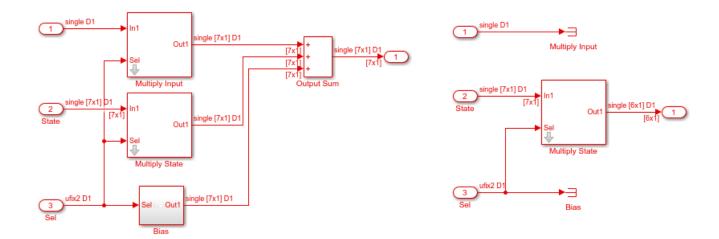

|    | Improved optimizations for conditional subsystems                                                                  | 2-16         |

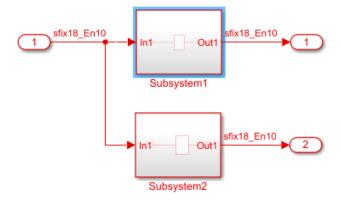

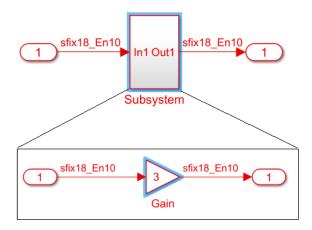

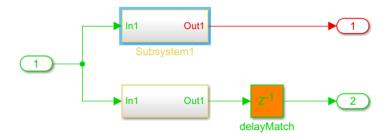

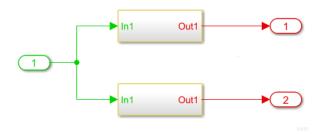

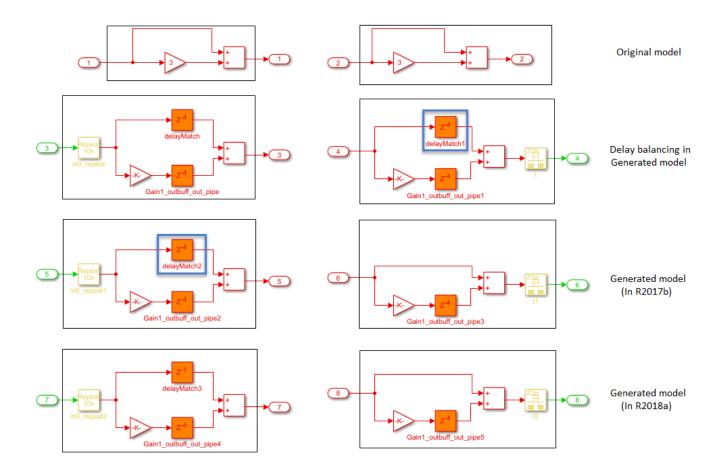

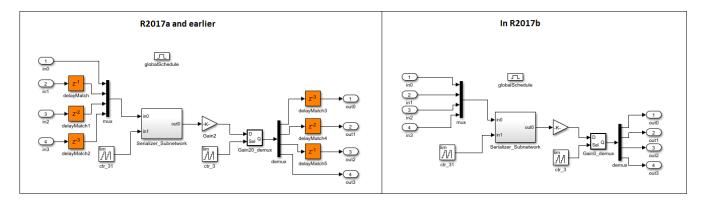

|    | Delay-balancing behavior standardization in BalanceDelays=off network                                              |              |

|    |                                                                                                                    | 2-17         |

|    | Lookup Table blocks mapping to RAM and adaptive pipelining                                                         | 2-17         |

|    |                                                                                                                    |              |

| ΙP | Core Generation and Hardware Deployment                                                                            | 2-18         |

|    |                                                                                                                    |              |

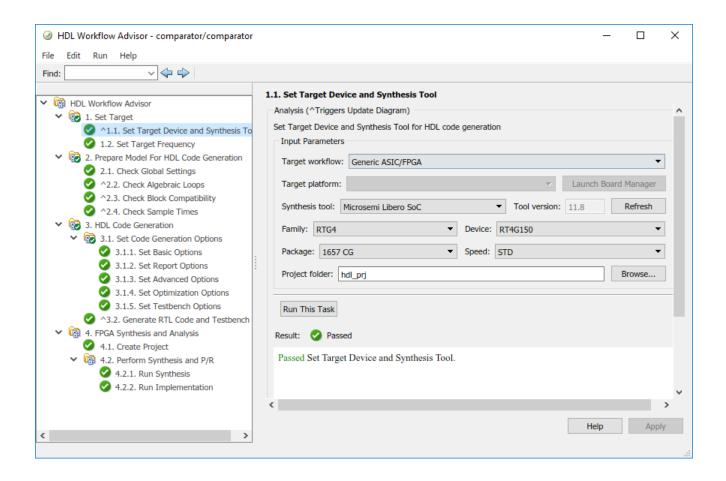

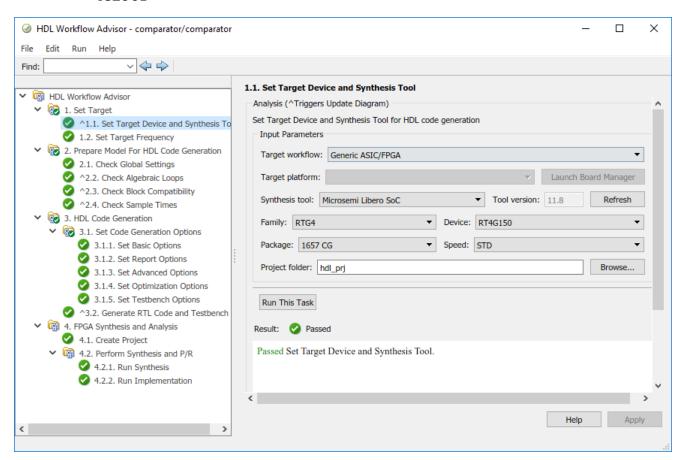

|    | Microsemi Libero System On A Chip (SoC) support for IP core generation                                             | 2 10         |

|    | workflow                                                                                                           | 2-18         |

|    | MATLAB Prototyping API Enhancements: Support complex data in AXI4                                                  | 2-18         |

|    | Stream Interface and input register readback in AXI4 Interface                                                     | 2-18<br>2-18 |

|    | Upgrade to Intel Quartus Pro 20.2                                                                                  | 2-18<br>2-18 |

|    | Inserted JTAG AXI Master at fixed frequency to avoid timing issue Unsupported tool version in HDL workflow advisor | 2-18<br>2-19 |

|    | Multicycle path constraint packaging for IP core                                                                   | 2-19<br>2-19 |

|    | HDL Coder Workflow Advisor: Option to expose DUT clock enable port and                                             | 4-19         |

|    | clock enable output port                                                                                           | 2-19         |

|    | Devicetree generation for IP cores                                                                                 | 2-19         |

|    | 20.100000 gonoravion for it 00100                                                                                  |              |

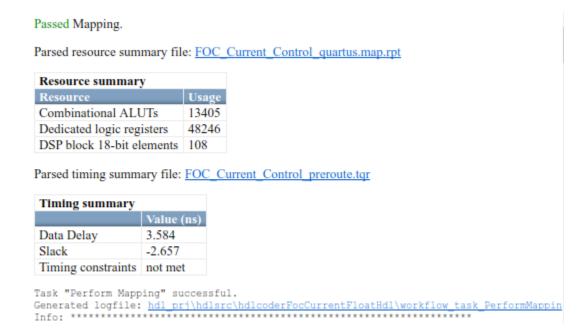

| object                                                                                                                                                                                                                                                                          | n  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| HDL Coder Workflow Advisor: Resource and timing report enhancement                                                                                                                                                                                                              |    |

| Data type for Speedgoat PCIe Interface: Map bus data types to Speedgoat                                                                                                                                                                                                         |    |

| PCIe Interface                                                                                                                                                                                                                                                                  |    |

| Simscape Hardware-in-the-Loop Workflow                                                                                                                                                                                                                                          |    |

| Support multiple solver times in Simscape models Enable FPGA parameters in the protected model                                                                                                                                                                                  |    |

| R2                                                                                                                                                                                                                                                                              | 20 |

| Model and Architecture Design                                                                                                                                                                                                                                                   |    |

| Half precision floating-point example for Field-Oriented Control algorithm                                                                                                                                                                                                      |    |

| Comments tab in Global Settings pane and option to disable comments HDL Code Advisor check for file extension based on target language Hard Floating Point Support using Intel Quartus Pro                                                                                      |    |

| Block Enhancements                                                                                                                                                                                                                                                              |    |

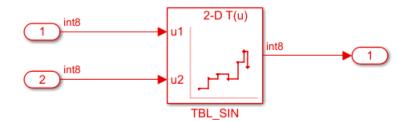

| Enhancement to parameterized HDL code generation for 1-D and 2-D mas values                                                                                                                                                                                                     |    |

| partitioning of mask parameters                                                                                                                                                                                                                                                 |    |

| Count hit port for HDL Counter block to indicate when count value resets                                                                                                                                                                                                        |    |

| 3-D lookup table support  HDL Code Generation for Data Type Conversion block supports enumerate data types  Enhancement to HDL code generation for Sqrt block                                                                                                                   | ed |

| New HDL-optimized Simulink blocks for reciprocal, divide, and modulo Reduced HDL resource utilization in fixed-point matrix library blocks Wireless HDL Toolbox Reference Applications: Implement 5G NR MIB recovery for FR2, OFDM interleaver and deinterleaver, and WLAN time | •  |

| and frequency synchronization                                                                                                                                                                                                                                                   |    |

|      | algorithms that require random access to memory (requires SoC Blockset                                                                    | ;<br><b>3-</b> 7 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|      | product)                                                                                                                                  | 3-7              |

|      | Functionality being removed or changed                                                                                                    | 3-8              |

| Coc  | de Generation and Verification                                                                                                            | 3-9              |

|      | Improvement to HDL code generated for Stateflow Moore Chart blocks                                                                        | 2.4              |

|      | Stateflow Chart property Initialize Outputs Every Time Chart Wakes Up cleared for HDL code generation                                     | 3-9<br>3-9       |

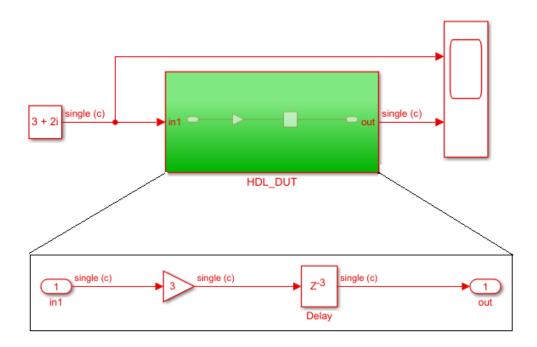

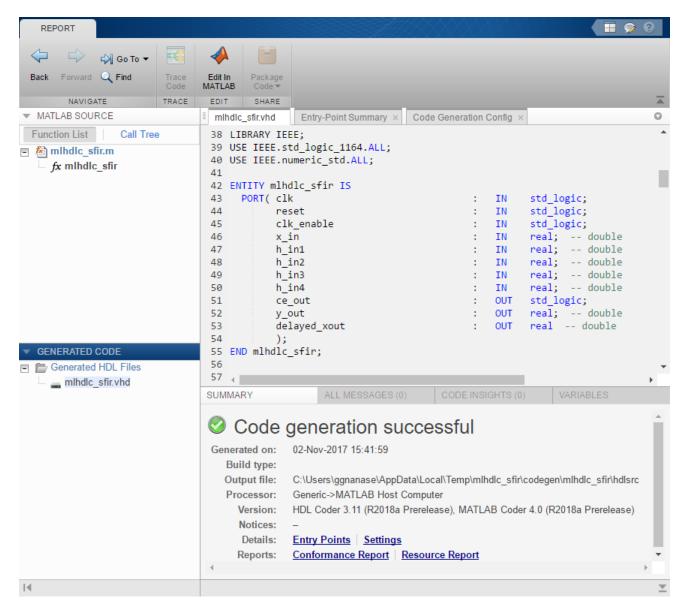

|      | architecture                                                                                                                              | 3-9              |

| Spe  | eed and Area Optimizations                                                                                                                | <b>3-1</b> 1     |

|      | Improved delay balancing support for multiple instances of atomic subsystems                                                              | 3-11             |

|      | Improved streaming in presence of scalar expanded constants Enhancement to optimization that removes redundant logic for atomic           | 3-11             |

|      | subsystems and model references                                                                                                           | 3-11<br>3-11     |

|      | Adaptive pipelining optimization disabled on model by default Generation of target-specific timing databases for critical path estimation | 3-11             |

|      |                                                                                                                                           | 3-12             |

| IP ( | Core Generation and Hardware Deployment                                                                                                   | <b>3-1</b> 3     |

|      | Updates to supported software                                                                                                             | 3-13             |

|      | interfaces in IP Core generation                                                                                                          | 3-13<br>3-13     |

|      | FPGA Data Capture integration with IP Core Generation workflow for                                                                        | 3-14             |

|      | generic Xilinx and generic Intel targets                                                                                                  | 3-14             |

|      | rate DUT ports                                                                                                                            | 3-14<br>3-15     |

|      | than 128 bits on AXI4-Stream data ports                                                                                                   | 3-15             |

|      | interfaces and external ports                                                                                                             | 3-15             |

|      | Interface option to customize initial value of AXI4 Master and AXI4 Stream registers                                                      | 3-15             |

| Sin  | nscape Hardware-in-the-Loop Workflow                                                                                                      | 3-17             |

|      | Partitioning solver: Use partitioning solver to generate HDL code from nonlinear models                                                   | 3-17             |

|      | Optimal value of oversampling factor automatically set on HDL implementation model                                                        | 3-17             |

| Model and Architecture Design                                                                                                                                                                                                                                                                                                                                                                                                                            | 4                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| <ul> <li>Half-Precision Native Floating Point: Generate target-independent synthesizable RTL code from half-precision floating-point models</li> <li>HDL code generation for lookup tables that have floating-point types</li> <li>HDL Code Advisor check for blocks that introduce latency with fixed-point</li> </ul>                                                                                                                                  | 4                     |

| types                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4                     |

| Block Enhancements                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4                     |

| Optimized Square Root: Generate high-frequency fixed-point HDL implementation of square root operations                                                                                                                                                                                                                                                                                                                                                  | 4                     |

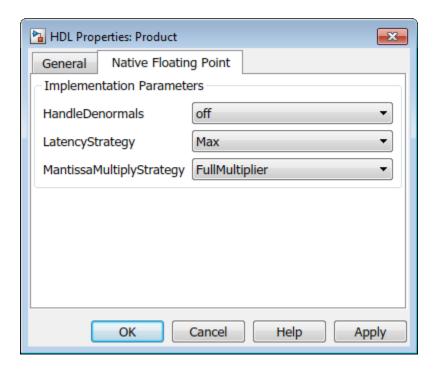

| Modulo option for HDL Counter block  HDL code generation for Scoped tag visibility for Goto block  Product block enhancements for HDL code generation  5G NR HDL MIB Recovery Reference Application: Implement 5G NR MIB recovery subsystem on FPGA or ASIC  OFDM Transmitter and Receiver Reference Applications: Implement custom OFDM wireless communication system on FPGA or ASIC  HDL-optimized FIR Decimation block and System object: Downsample | 4<br>4<br>4<br>4<br>4 |

| signals using a FIR decimation filter with a hardware-friendly interface and architecture                                                                                                                                                                                                                                                                                                                                                                | 4                     |

| algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4                     |

| streaming video                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4                     |

| Code Generation and Verification                                                                                                                                                                                                                                                                                                                                                                                                                         | 4                     |

| Option to scalarize vector ports only at DUT level in VHDL code HDL code generation for models that have comment through blocks HDL code generation for models that have Subsystem Reference blocks                                                                                                                                                                                                                                                      | 4                     |

| Enhancement to HDL code generation for nontop DUT                                                                                                                                                                                                                                                                                                                                                                                                        | 4<br>4<br>4<br>4<br>4 |

| Speed and Area Optimizations                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-                    |

| Option to control removal of unused ports in generated HDL code                                                                                                                                                                                                                                                                                                                                                                                          | 4-                    |

| Hierarchy flattening report Optimization enhancements for Sum of Elements and MinMax blocks                                                                                                                                  | 4-10<br>4-10               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| IP Core Generation and Hardware Deployment                                                                                                                                                                                   | 4-11                       |

| Rapid prototyping of HDL IP core by using software interface script Interface option to customize initial value of AXI4 slave registers Generation of HDL IP cores that have greater than 128 bits on internal IO            | 4-11<br>4-11               |

| interface                                                                                                                                                                                                                    | <b>4-12</b><br><b>4-12</b> |

| Intel Quartus Pro SoC Targeting: Generate generic HDL IP core or integrate IP core into Intel reference designs                                                                                                              |                            |

| Simscape Hardware-in-the-Loop Workflow                                                                                                                                                                                       | 4-14                       |

| Automatic replacement of Simscape subsystem with state-space implementation                                                                                                                                                  |                            |

| Advisor                                                                                                                                                                                                                      | 4-14                       |

| Dunlingto configurations removed in generated IDI implementation model                                                                                                                                                       | 4-14                       |

| Duplicate configurations removed in generated HDL implementation model                                                                                                                                                       | 4-14                       |

| ·                                                                                                                                                                                                                            | 4-14<br>020a               |

| ·                                                                                                                                                                                                                            |                            |

| R20                                                                                                                                                                                                                          | )20a                       |

| Model and Architecture Design                                                                                                                                                                                                | <b>)20a</b><br>5-2<br>5-2  |

| Model and Architecture Design  Additional HDL modeling guidelines added to documentation Functionality being removed or changed  Block Enhancements  Inverse of streaming matrix input using Gauss-Jordan elimination method | 5-2<br>5-2<br>5-2<br>5-3   |

| Model and Architecture Design  Additional HDL modeling guidelines added to documentation Functionality being removed or changed  Block Enhancements                                                                          | 5-2<br>5-2<br>5-2          |

| HDL-optimized NCO for high speed applications (requires HDL Coder for                                                 |              |

|-----------------------------------------------------------------------------------------------------------------------|--------------|

| code generation)                                                                                                      | 5-6          |

| algorithm                                                                                                             | 5-6          |

| that use line buffer memory                                                                                           | 5-6          |

| Code Generation and Verification                                                                                      | 5-8          |

| Obfuscated HDL Output: Generate plain-text HDL code with randomized                                                   | <b>-</b> 0   |

| identifier names                                                                                                      | 5-8<br>5-8   |

| Speed and Area Optimizations                                                                                          | 5-11         |

| Upsampling signals without latency using Rate Transition blocks                                                       | 5-11         |

| IP Core Generation and Hardware Deployment                                                                            | 5-12         |

| AXI4-Stream for MIMO: Generate IP cores with multiple input and output channels                                       | 5-12         |

| High-Bandwidth AXI Master: Generate IP cores with up to 512 bits on AXI4 Master data ports                            | 5-12<br>5-12 |

| parameters                                                                                                            | 5-13         |

| Option to insert JTAG MATLAB AXI Master in standalone FPGA reference designs (requires HDL Verifier)                  | 5-14         |

| socExportReferenceDesign Function: Automatically create reference design (requires SoC Blockset)                      | 5-14         |

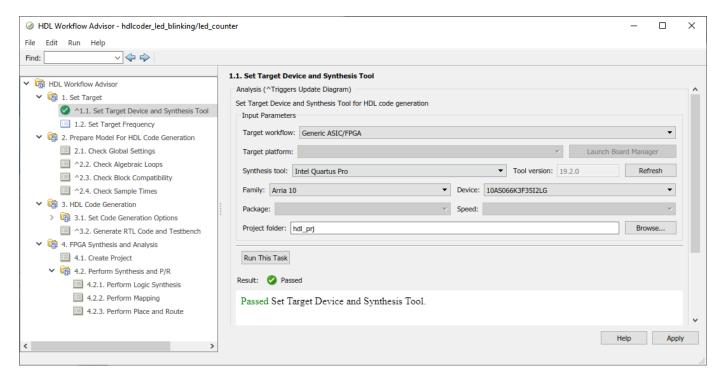

| Intel Quartus Pro Targeting: Synthesize and implement generated HDL code on Intel FPGAs by using HDL Workflow Advisor | <b>5-14</b>  |

| Speedgoat IO Modules IO331 and IO331-6 being removed                                                                  | 5-15<br>5-15 |

| Simscape Hardware-in-the-Loop Workflow                                                                                | 5-17         |

| Simscape Hardware-in-the-Loop: Generate HDL implementation model from multiple Simscape networks                      | 5-17         |

| Reduction in latency of HDL implementation model generated from Simscape algorithm                                    | 5-17         |

| Improvement to single-rate resource sharing in HDL implementation model                                               | 5-17         |

|                                                                                                                       |              |

| R20                                                                                                                   | 10h          |

| K20                                                                                                                   | TSD          |

| Model and Architecture Design                                                                                         | 6-2          |

| HDL code generation for MATLAB Function block in native floating-point mode                                           | 6-2          |

| HDL Coder contextual tab on Simulink Toolstrip                                                                        | 6-2          |

| Ι     | Documentation revision for HDL code generation support for blocks                                                  | 6           |

|-------|--------------------------------------------------------------------------------------------------------------------|-------------|

| Block | Enhancements                                                                                                       | 6           |

| Ι     | Discrete FIR Filter HDL Optimized block supports complex coefficient values                                        | 6           |

| F     | Process high-frame-rate or high-resolution video with multipixel streaming interface                               | 6           |

| (     | DFDM Demodulator, Convolutional Encoder, and Puncturer blocks for custom wireless communication protocols          | 6           |

|       | Symbol Demodulator and 1536-point FFT for LTE and NR (5G) designs                                                  | 6           |

|       | HDL-optimized CIC Decimation block and System Object Enhancements to fixed-point Division and Reciprocal operators | 6           |

| F     | FWFT mode for HDL FIFO block                                                                                       | 6           |

|       | HDL code generation enhancements to matrix support                                                                 | 6           |

| I     | HDL code generation for partitioning of mask parameters in For Each                                                | 6           |

| I     | Subsystem                                                                                                          | 6<br>6      |

| Code  | Generation and Verification                                                                                        | 6           |

| Ţ     | UltraRAM mapping in Xilinx devices                                                                                 | 6           |

| Speed | d and Area Optimizations                                                                                           | 6           |

|       | Enhanced optimization support for MATLAB Function block                                                            | 6           |

| F     | blocks                                                                                                             | 6<br>6      |

| IP Co | re Generation and Hardware Deployment                                                                              | 6           |

|       | Optimization of AXI4 slave readback logic                                                                          | 6           |

| (     | workflow                                                                                                           | 6           |

| F     | (requires HDL Verifier)                                                                                            | 6           |

| Ţ     |                                                                                                                    | 6-í         |

| Simso | cape Hardware-in-the-Loop Workflow                                                                                 | <b>6-</b> 2 |

| F     | Enhanced HDL implementation model for Simscape and Simulink plant in                                               | <b>6-</b> 1 |

| ľ     | Number display of differential and algebraic variables in Simscape HDL                                             |             |

| 5     | Workflow Advisor                                                                                                   | <b>5-</b>   |

|       | discretizing equations                                                                                             | 6-1<br>6-1  |

| Model and Architecture Design                                                                                 | 7-2               |

|---------------------------------------------------------------------------------------------------------------|-------------------|

| Protected Model Code Generation: Share protected Simulink models with the option to allow HDL code generation | 7-2               |

| Additional block support with double-precision native floating-point code                                     | 7-2               |

| generation                                                                                                    | 7-3<br>7-3        |

| HDL Coder contextual tab in Simulink Toolstrip                                                                | 7-3<br>7-3        |

| HDL Coder Modeling Guidelines in Documentation                                                                | 7-4               |

| Block Enhancements                                                                                            | 7-5               |

| Streaming Matrix Multiply and Streaming Matrix Inverse Reference                                              |                   |

| Applications                                                                                                  | 7-5               |

| Partition Offset parameter support in For Each Subsystem block Enhancements to Assignment and Selector blocks | 7-5<br>7-5        |

| Enhancements to Discrete FIR Filter HDL Optimized block and frame-based                                       |                   |

| Discrete FIR Filter block                                                                                     | 7-6               |

| LTE Reference Applications: Transmitter example and TDD support for SIB recovery                              | 7-6               |

| OFDM Modulator block and LTE and 5G Symbol Modulator blocks                                                   | 7- <b>6</b>       |

| Increased kernel size limits for Image Filter block                                                           | 7-7               |

| Code Generation and Verification                                                                              | 7-8               |

| Customization of constant name in VHDL code generated for Lookup Table                                        |                   |

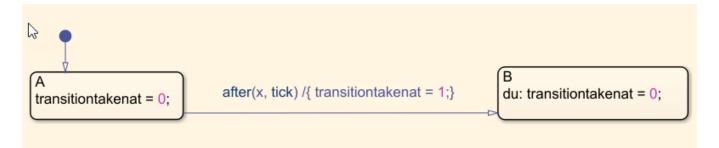

| dataOptimized counters in generated HDL code for Stateflow temporal logic                                     | 7-8               |

| HDL Coder Workflow: Enhanced options for model generation                                                     | 7-8<br>7-9<br>7-9 |

| Speed and Area Optimizations                                                                                  | 7-12              |

| Improvements to element-wise matrix transformation                                                            | 7-12              |

| Optimization of unconnected port for removing redundant logic in design                                       | 7-12              |

|                                                                                                               | <b>-</b> 40       |

| IP Core Generation and Hardware Deployment                                                                    | 7-13              |

| DUT AXI4 slave interface connection to multiple AXI Master interfaces in                                      | _ 40              |

| reference designs                                                                                             | 7-13<br>7-13      |

| Generation of HDL IP core without AXI4 slave interfaces                                                       | <b>7-13</b>       |

| Minimization of clock analysis arms to ID Core Consertion wealther                                            | 7-14              |

| Minimization of clock enable signals in IP Core Generation workflow Updates to supported software             | 7-14<br>7-14      |

| Simscape Hardware-in-the-Loop Workflow                                                                        | 7-15              |

| 1                                                                                                                                                                                                   | 7-15         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 1                                                                                                                                                                                                   | 7-15<br>7-15 |

|                                                                                                                                                                                                     |              |

| R20:                                                                                                                                                                                                | 18b          |

|                                                                                                                                                                                                     |              |

| Model and Architecture Design                                                                                                                                                                       | 8-2          |

| Verilog Import: Import synthesizable Verilog code and generate Simulink model                                                                                                                       | 8-2          |

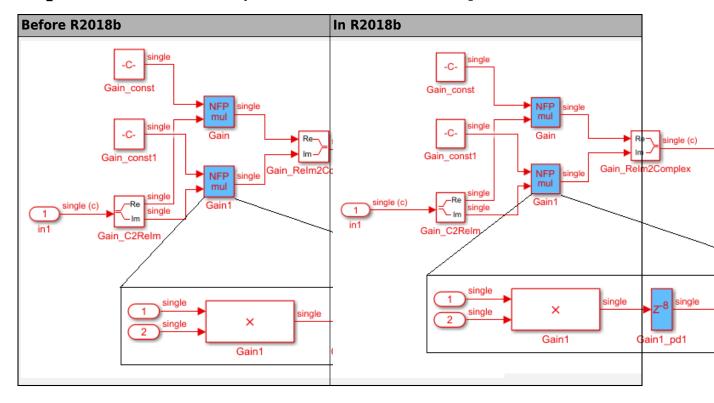

| synthesizable RTL from double-precision floating-point models Custom latency specification for native floating-point operators Enhancements to supported blocks and complex data types with single- | 8-2<br>8-2   |

| precision native floating-point                                                                                                                                                                     | 8-3<br>8-3   |

| Block Enhancements                                                                                                                                                                                  | 8-5          |

| Enhancements to matrix support for HDL code generation HDL code generation support for Probe block and blocks that detect change                                                                    | 8-5          |

| in input signal value                                                                                                                                                                               | 8-5<br>8-5   |

| resets setting                                                                                                                                                                                      | 8-5          |

| (requires LTE HDL Toolbox)                                                                                                                                                                          | 8-6          |

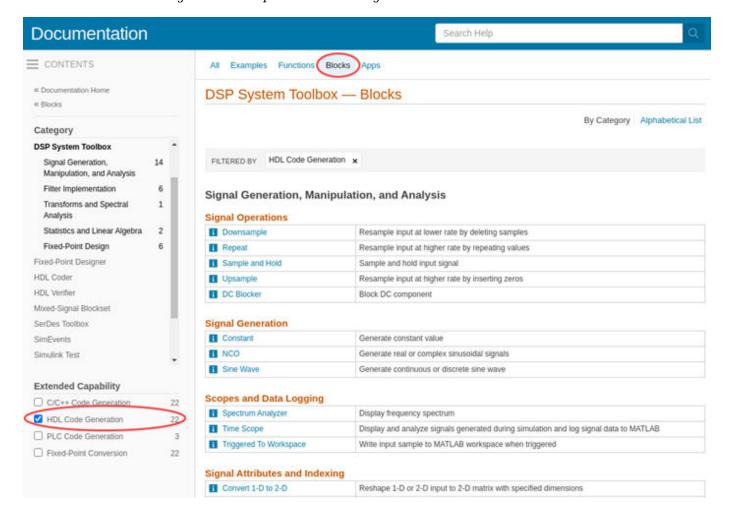

| (requires DSP System Toolbox)                                                                                                                                                                       | 8-6          |

| (requires DSP System Toolbox)                                                                                                                                                                       | 8-6          |

| Code Generation and Verification                                                                                                                                                                    | 8-8          |

| Test Point Integration with FPGA Data Capture: Use FPGA data capture to specify signals to be captured during FPGA testing by using Test Points in Simulink                                         | 8-8          |

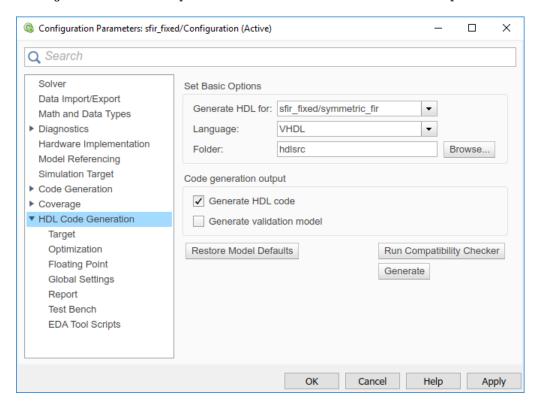

| User-Interface Improvements to HDL Workflow Advisor and HDL Code Generation Pane in Configuration Parameters Dialog Box                                                                             | 8-8          |

| Speed and Area Optimizations                                                                                                                                                                        | 8-11         |

| Streaming operation modes of Multiply-Accumulate block                                                                                                                                              | 8-11<br>8-11 |

| Different output latencies for designs with clock-rate pipelining enabled at output ports                                                                                                           | 8-11         |

| IP Core Generation and Hardware Deployment                                                                                                                                                                                                                                                                                                                                | 8-14                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

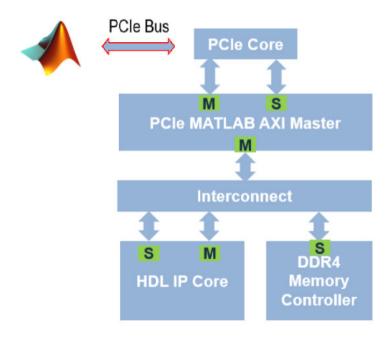

| Xilinx Zynq UltraScale+ MPSoC Targeting: Select from predefined targets and reference designs to generate code for MPSoC devices Multirate IP Core Generation: Target AXI4-Stream and AXI4 Master interfaces for designs with multiple sample rates PCIe MATLAB as AXI Master with External DDR4 Memory Access reference design for Intel Arria10 GX FPGA Development kit | 8-14<br>8-14<br>8-15<br>8-15<br>8-16<br>8-17<br>8-17 |

| Simscape Hardware-in-the-Loop Workflow                                                                                                                                                                                                                                                                                                                                    | 8-18                                                 |

| Hardware Acceleration of Plant Models: Generate HDL code from Simscape Electrical switched linear models                                                                                                                                                                                                                                                                  | 8-18                                                 |

| R20                                                                                                                                                                                                                                                                                                                                                                       | 18a                                                  |

|                                                                                                                                                                                                                                                                                                                                                                           |                                                      |

| Model and Architecture Design                                                                                                                                                                                                                                                                                                                                             | 9-2                                                  |

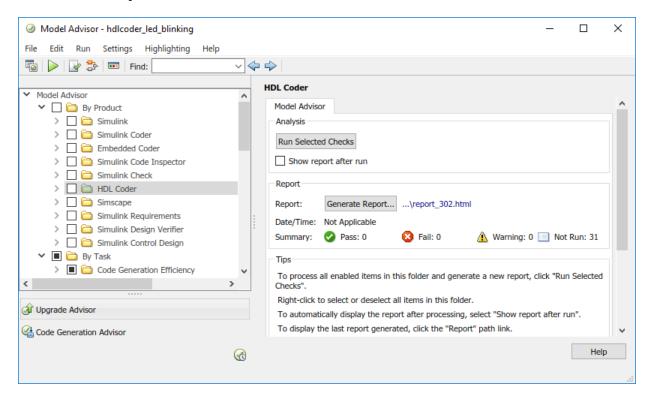

| HDL Model Checker integrated with Model Advisor                                                                                                                                                                                                                                                                                                                           | 9-2<br>9-2                                           |

| Floating Point mode                                                                                                                                                                                                                                                                                                                                                       | 9-3<br>9-3                                           |

| HDL code generation support for all rounding modes of Data Type Conversion block in Native Floating Point mode Floating-point control for Multiport Switch and Selector blocks                                                                                                                                                                                            | 9-3<br>9-4                                           |

| Block Enhancements                                                                                                                                                                                                                                                                                                                                                        | 9-5                                                  |

| Matrix Support: Generate HDL code directly from two-dimensional matrix data types and operations                                                                                                                                                                                                                                                                          | 9-5<br>9-5<br>9-5                                    |

| LTE HDL Toolbox)                                                                                                                                                                                                                                                                                                                                                          | 9-6<br>9-6                                           |

| Toolbox)                                                                                                                                                                                                                                                                                                                                                                  | 9-6<br>9-7                                           |

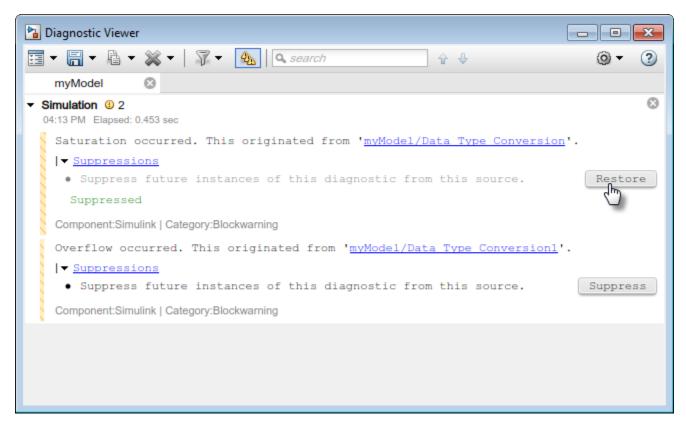

| Critical Path Estimation with Native Floating Point: Report critical path for designs with single-precision floating-point operations Simplification of constant operations and other optimizations for fixed-point and floating-point arithmetic operations | 9-7<br>9-7<br>9-8<br>9-11<br>9-11<br>9-11    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|                                                                                                                                                                                                                                                              | 9-13                                         |

| AXI4-Stream for Intel FPGA: Generate IP cores with the AXI4-Stream interface targeting Intel FPGAs                                                                                                                                                           | 9-13<br>9-13<br>9-13<br>9-14<br>9-14<br>9-14 |

| Model and Architecture Design  Model Advisor Checks: Check and update your Simulink model for HDL code generation compatibility                                                                                                                              | 10-2<br>10-2<br>10-2<br>10-3<br>10-3         |

| Block-level latency customization for Discrete Transfer Function and Discrete Time Integrator blocks with native floating-point             | 10-4                    |

|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Block Enhancements                                                                                                                          | 10-5                    |

| Minimum Resource FFT/IFFT: Reduce resource usage with the Burst Radix 2 architecture of the HDL-Optimized FFT (requires DSP System Toolbox) |                         |

| Support for scalar addressing mode with vector data input to hdl.RAM System Object                                                          | 10-5<br>10-5            |

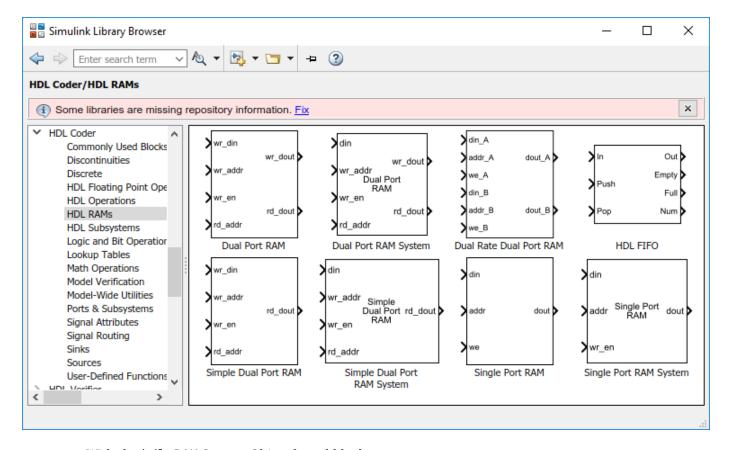

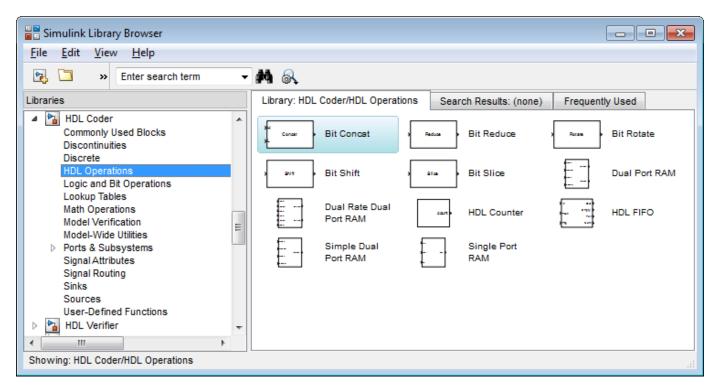

| New HDL RAMs Block Library and hdl.RAM System Object based blocks                                                                           | 10-5                    |

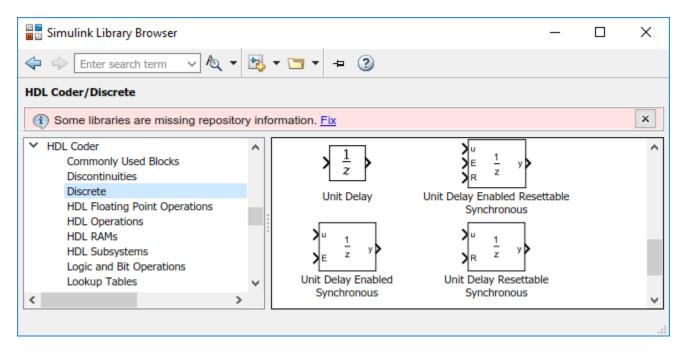

| Synchronous versions of Unit Delay blocks with reset and enable ports in Discrete block library                                             | 10-5                    |

| Bilateral filter, bird's-eye-view transform, and line buffer for vision applications                                                        | 10-0                    |

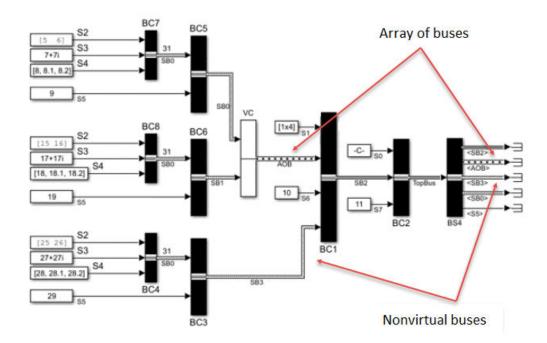

| HDL code generation support for Bus Element port blocks                                                                                     | 10-7                    |

| One-hot and two-hot encoding schemes for enumeration types Custom header and footer comments in generated HDL code                          | 10-7<br>10-8            |

| Code Generation and Verification                                                                                                            | 10-9                    |

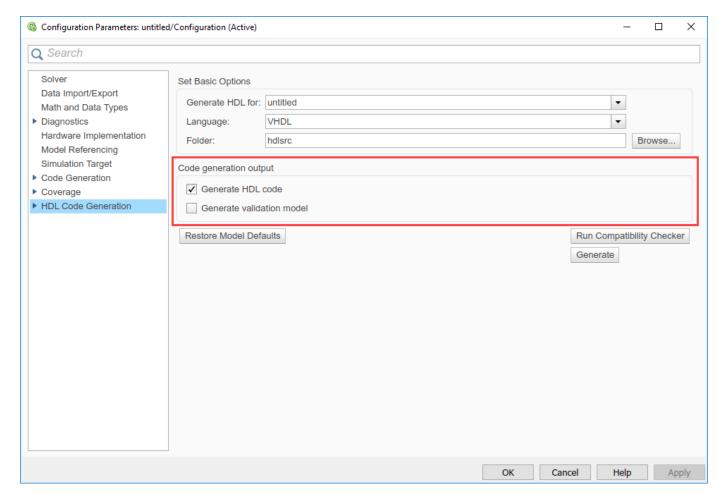

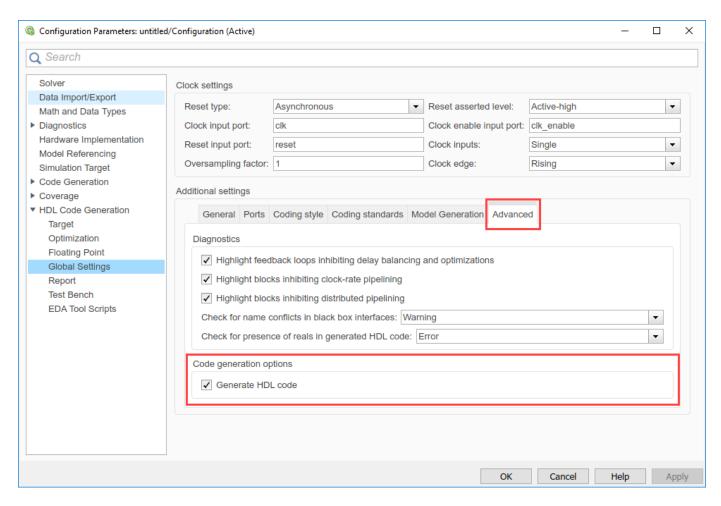

| Changes to HDL Code Generation Panel in Configuration Parameters Dialog Box                                                                 | <b>10-9</b>             |

| Speed and Area Optimizations                                                                                                                | 10-10                   |

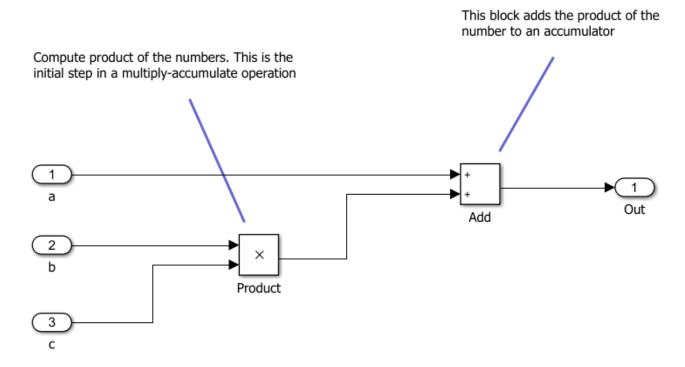

| Vector Input Multiply-Accumulate (MAC) Block: Map arithmetic operations efficiently to FPGA DSP slices                                      | 10-10                   |

| hierarchical boundaries                                                                                                                     | 10-10<br>10-10<br>10-11 |

| IP Core Generation and Hardware Deployment                                                                                                  | 10-12                   |

| AXI4 Master Interface: Facilitate communication between your design and external memory by using the AXI4 Master protocol for more flexible | 40.40                   |

| data access                                                                                                                                 | 10-12                   |

| IP core for DUT containing System Generator blocks INOUT port type support for External Port interface in IP Core Generation                | 10-12                   |

| workflow                                                                                                                                    | 10-12                   |

| in generated IP core                                                                                                                        | 10-12                   |

| J J                                                                                                                                         | 10-13<br>10-13          |

|                                                                                                                                             | 10-13                   |

| מס                                                                                                                                          | 017a                    |

| N20                                                                                                                                         | <b>JI/</b> (1)          |

| Model and Architecture Design                                                                                                               | 11-2                    |

| single-precision floating-point blocks supported for HDL code generation                                                                                                                        |                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Floating-Point Latency Customization at Block-Level                                                                                                                                             | 11-2<br>11-2        |

| Custom reference model prefix specification                                                                                                                                                     | 11-3<br>11-3        |

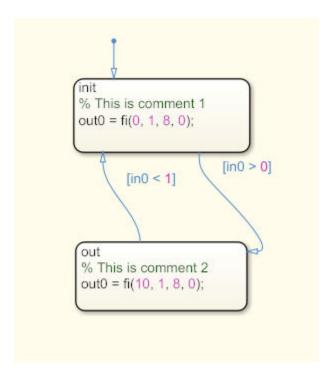

| Comments in HDL code for Simulink blocks with text annotations                                                                                                                                  | 11-4<br>11-4        |

| Block Enhancements                                                                                                                                                                              | 11-7                |

| For Each Subsystems: Reduce block replication and improve code reuse in HDL-targeted designs                                                                                                    | 11-7                |

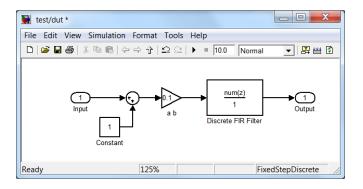

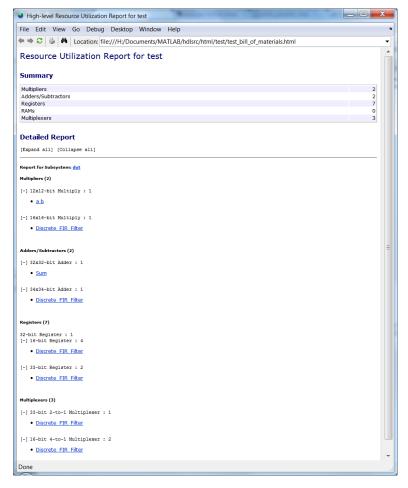

| HDL Optimized Filters: Model and generate optimized hardware implementations for FIR filters (requires DSP System Toolbox) HDL Channelizer Block and System Object: Isolate narrowband channels | 11-7                |

| from a wideband signal and generate HDL with efficient multiplier usage (requires DSP System Toolbox)                                                                                           | 11-7                |

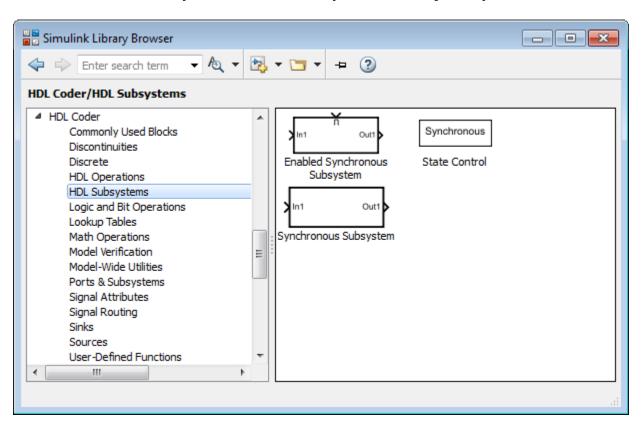

| FIR decimation algorithms by using frame input Enhancements to MATLAB Function block support in synchronous subsystems                                                                          | 11-7<br>11-8        |

| HDL Coder support for blocks that support bus signal treated as vector                                                                                                                          | 11-8                |

| Additional HDL Coder bus support                                                                                                                                                                | 11-9<br>11-9        |

| Code Generation and Verification                                                                                                                                                                | 11-10               |

| Native Floating-Point Testbench: Generate SystemVerilog DPI, cosimulation and FPGA-in-the-loop test benches with single-precision data types                                                    |                     |

| More fixed-size variable information in Fixed-Point Conversion step of HDL                                                                                                                      | 11-10<br>11-10      |

| Comments in generated HDL code for MATLAB System blocks                                                                                                                                         | 11-10<br>11-10      |

| properties                                                                                                                                                                                      | 11-11<br>J<br>11-11 |

|                                                                                                                                                                                                 | 11-11               |

| Speed and Area Optimizations                                                                                                                                                                    | 11-12               |

| 1 5 5                                                                                                                                                                                           | 11-12<br>11-12      |

| IP Core Generation and Hardware Deployment                                                                                                                                                      | 11-13               |

| Data Type Support for AXI4 Slave: Map floating-point signals and vector signals to AXI4 slave interfaces in IP core generation                                                                  | 11-13               |

| Incremental Vivado Synthesis: Enable IP caching for faster synthesis of Xilinx Vivado reference designs                                     | 11-13<br>11-14<br>11-14<br>11-14<br>11-14 |

|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| R2                                                                                                                                          | 2016b                                     |

| Model and Architecture Design                                                                                                               | 12-2                                      |

| Native Floating Point: Generate target-independent synthesizable RTL from                                                                   | m                                         |

| single-precision floating-point models                                                                                                      | 12-2                                      |